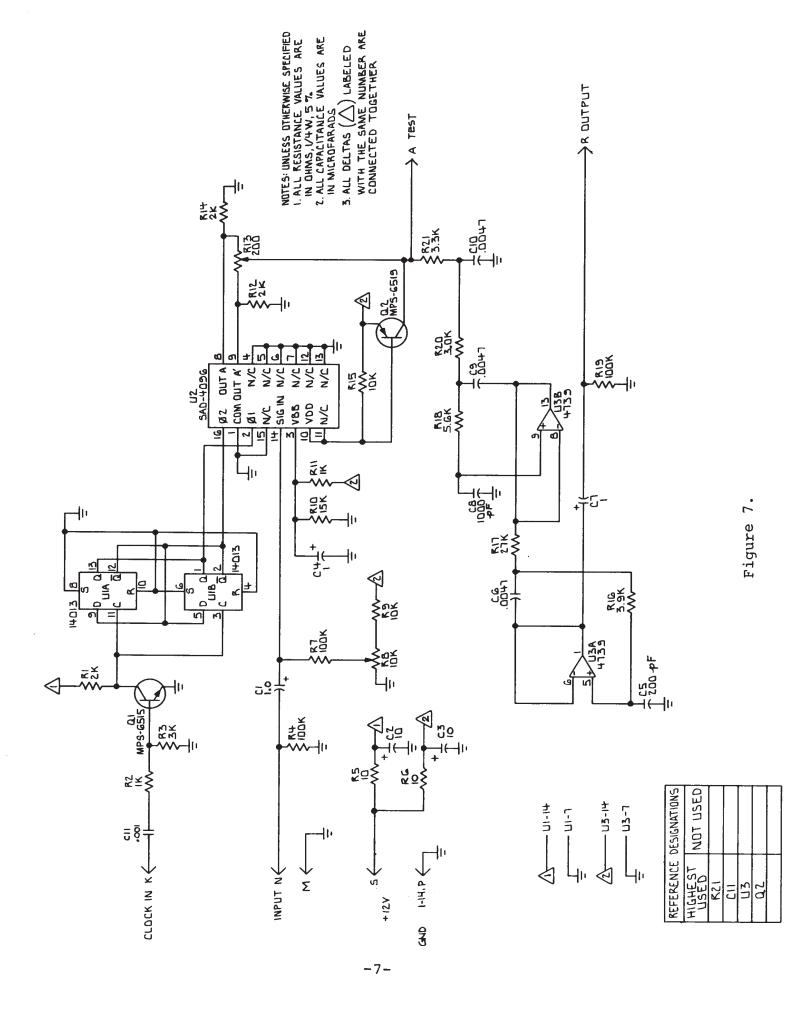

Typical Applications

Sound effects

Data buffering

Speech scramblers

Reverberation effects

ANALOG DELAY LINE

The SAD-4096 is a general purpose 4096-bucket (2048-sample) n-channel bucket-brigade audio delay line useful in applications where relatively long delay is desired, coupled with high performance. The signal is sampled at the clock rate, but the samples retain their analog values. Simple filtering applied at the output smooths the stairstep of samples to recover the analog wave form.

The delay is controlled by the clock frequency according to the relation  $T_D = 2048/f_c$ , so that a clock or sample rate of 40 KHz, for example, the delay is 51.2 milliseconds.

#### Key Features

2048 samples of audio signal delay

Wide dynamic range: S/N 70 db (unweighted)

Clock-Controlled Variable delay

Sample rates from 8 KHz to 1 MHz

Delays from 2 msec to 250 msec

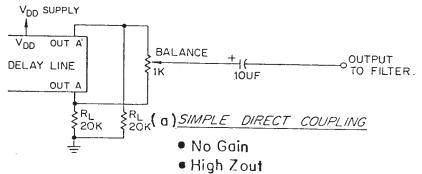

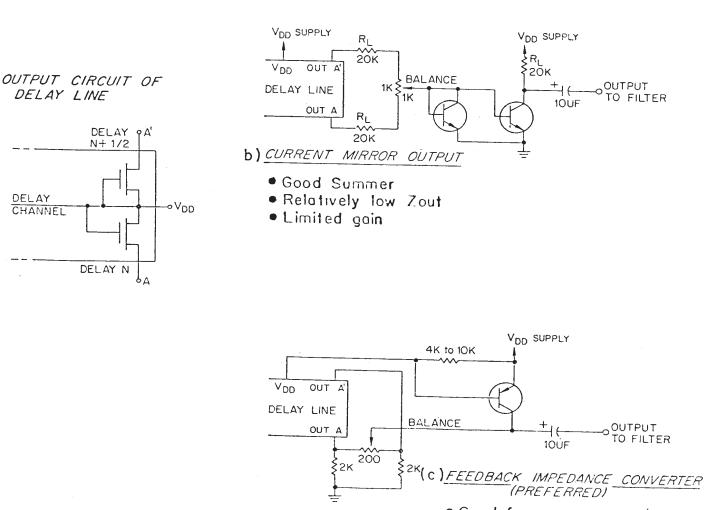

On-chip buffers provide full-wave output

18317

EG&G RETICON • 345 POTRERO AVENUE • SUNNYVALE, CALIFORNIA 94086 TELEPHONE: (408) 738-4266 • TWX 910-339-9343

### Absolute Maximun Ratings

| Voltage on any pin to common (pin 1) | -0.5 to +18 volts dc or peak           |  |  |

|--------------------------------------|----------------------------------------|--|--|

| Output Current                       | 5 milliamperes                         |  |  |

| Temperature (operating)              | $0^{\circ}$ to $70^{\circ}$ C          |  |  |

| Temperature (storage)                | -55 <sup>0</sup> to 125 <sup>0</sup> C |  |  |

Note: Long delays are limited by leakage to approximately 0.25 second, at  $25^{\circ}$  C at a clock rate of 8 KHz. At  $70^{\circ}$ C, the minimum sample rate rises to more than 250 KHz.

## Drive and Voltage Reguirements

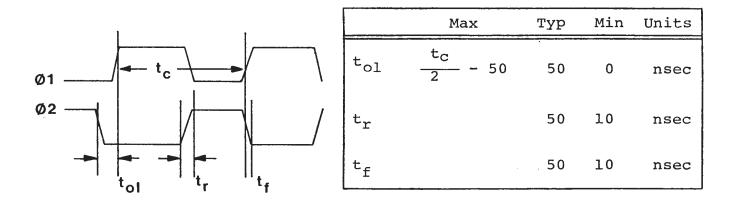

Normal voltage levels and limits are given in the specifications, Table I. The clock inputs are normally complementary square waves. The timing relationships are noncritical, so long as the crossing level is below the top quarter of the wave.

Figure 2. SAD-4096 Clock Timing Requirements

RETICON Corporation is a subsidiary of EG&G, Inc., Wellesley, Massachusetts. Copyright RETICON Corporation 1978. Contents may not be reproduced in whole or in part without the written consent of RETICON Corporation. Specifications are subject to change without notice. Printed in U.S.A.

-2-

Information furnished herein is believed to be accurate and reliable. However, no responsibility is assumed by RETICON Corporation for its use, nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of RETICON Corporation.

#### TABLE I

| Symbol                                   | Function                          | Min  | Typical            | Max                                   | Units     |

|------------------------------------------|-----------------------------------|------|--------------------|---------------------------------------|-----------|

| V <sub>DD</sub>                          | Output Supply                     | 8    | 12-15              | 18                                    | Volts dc  |

| V <sub>BB</sub>                          | CTD Interstage<br>Bias Voltage    | 8    | V <sub>ØH</sub> −1 | 12                                    | Volts dc  |

| V <sub>ØlH</sub> ,<br>V <sub>Ø2H</sub> , | CID Clock<br>Amplitude            | -0.3 | 0                  | 0.5                                   | Volts p   |

| v <sub>ø1</sub> н,<br>v <sub>ø2</sub> н, |                                   | 8(1) | 12–15              | 18                                    | Volts p   |

| V <sub>IB</sub>                          | Input Bias                        | 0.3  | 3 <sup>(2)</sup>   | 6                                     | Volts dc  |

| Vin                                      | (V <sub>bb</sub> = 11.5<br>volts) |      | 2                  |                                       | Volts p-p |

| CØ                                       | Clock Line<br>Capacitance         |      | 1000               | · · · · · · · · · · · · · · · · · · · | pf        |

| C <sub>in</sub>                          | Input<br>Capacitance              |      |                    | 2                                     | pf        |

| fc                                       | Clock or sample<br>rate           | 8    | 100                | 2000                                  | KHz       |

# SAD-4096 Electrical Specifications (25<sup>O</sup>C)

#### Footnotes for Table I

- The device is operable to clock and supply voltages as low as 5 volts, but at substantially reduced signal levels.

- (2) Input bias is dependent on the particular values of  $V_{BB}$ ,  $V_{\emptyset}$  and  $V_{DD}$ , so that adjustment provision should be made to fit the circumstances used.

- (3) WARNING: Observe MOS Handling and Operating Procedures. Maximum rated supply voltages must not be exceeded. Use decoupling networks to suppress power supply turn on/off transients, ripple and switching transients. Do not apply independently powered or AC coupled signals or clocks to the chip with power off as this will forward bias the substrate. Damage may result if external protection precautions are not taken.

-3-

Figure 3. Effect of Load Impedance on Signal Output Level.

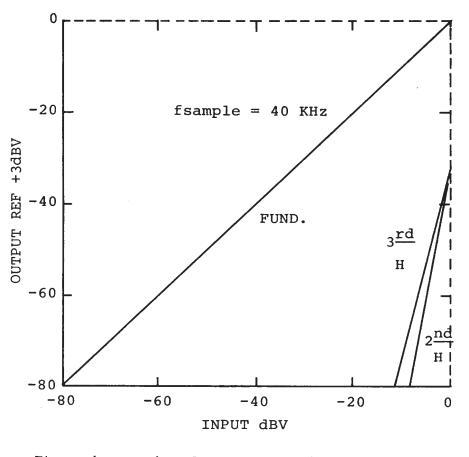

Figure 4. Signal and Harmonic Output Levels versus Input Level.

-4-

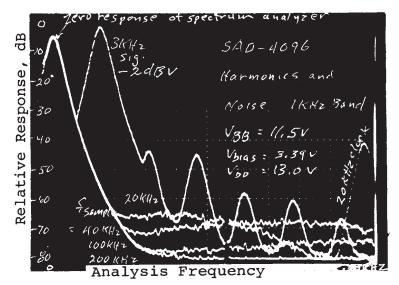

Spectrum Analyzer Response Showing a 3 KHz Signal and Four Traces of Noise Background at Sample Rates of 20, 40, 100 and 200 Kilohertz.

Note:

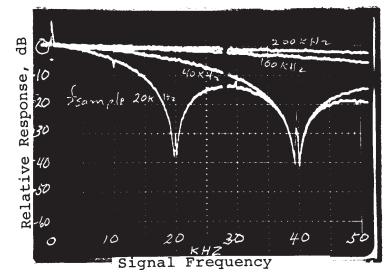

Due to the  $\frac{\sin x}{x}$ sampling, the response is down 3.92 db at the Nyquist frequency.

Figure 8.

DELAY

- Good frequency response

- Low Zout

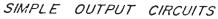

- Simple circuit