NOTES

# SILICON SIGNAL DIODES & SNAP DIODES

17

## SILICON SIGNAL DIODES

Semiconductor diodes are used extensively in all types of electronic circuitry. Many of the chapters in this manual illustrate applications in which diodes are used, from detectors in radio receivers to gating and logic elements in computer circuits. The first semiconductor diodes, made before the invention of the transistor, were silicon point contact diodes used as detectors in radar receivers. Later, germanium point contact diodes and gold bonded diodes were introduced which could be used in a variety of applications. The demand for high operating temperatures and low leakage currents led to the development of the silicon alloy junction diode and the silicon diffused mesa diode. Reliability and superior electrical characteristics of the silicon diode together with declining prices has caused it to be used in place of germanium diodes in an increasing number of applications.

In addition, by utilizing various properties of silicon diodes several special types of diodes have evolved, i.e., varactor diodes, stabistor diodes, snap diodes, etc. The snap diode is of particular interest because it makes possible highly efficient harmonic generators, and also pulse generators having high repetition rates with extremely short transition times (as low as 0.1 nanoseconds).

#### PLANAR EPITAXIAL PASSIVATED SILICON DIODE

Silicon diodes can be made using any of the transistor fabrication techniques including alloying, growing, meltback, or diffusion. But on the basis of inherent reliability and overall electrical parameters the *planar epitaxial passivated* (PEP) diode structure has proven superior to all others. Some of the significant advantages of the PEP silicon diode include

- 1. High forward conductance due to use of epitaxial material.

- 2. Low, uniform, leakage currents due to passivated surfaces.

- 3. Low capacitance due to small planar junction.

- 4. Low reverse recovery time due to accurate control of lifetime with gold doping.

- 5. High reliability due to passivation and rugged mechanical structure.

Fabrication of the diode starts with a wafer of low resistivity single crystal silicon. A thin epitaxial layer of high resistivity silicon is grown on the wafer. A layer of silicon oxide is formed over the entire wafer and the oxide is removed from small circular "windows" by means of photographic techniques. The planar junctions are then diffused through the windows in the oxide. Gold is plated on the back of the wafer and diffused into the wafer at a temperature determined by the required reverse recovery time. The wafer is cut into pellets each forming a complete diode, and contacts are made to the front and back of the pellets. Each pellet is then mounted in a glass package and the package is sealed.

Formation of the junction under a stable silicon oxide layer results in a passivated diode which is immune to contaminants which plague other types of silicon diodes. The effectiveness of the passivation is substantiated by a tight distribution of reverse leakage current, a parameter which is usually very sensitive to surface conditions, and by the close correlation between the measured values of the electrical parameters and the theoretical values. The use of an epitaxial structure reduces the bulk resistance of the diode and thus makes it possible to achieve simultaneously a high conductance together with a low capacitance and a low reverse recovery time.

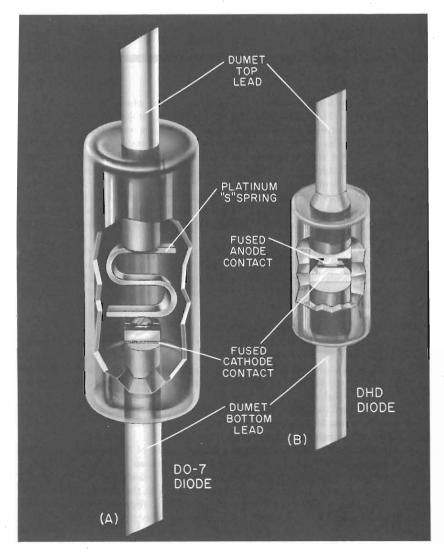

CUT-AWAY VIEW OF PEP SILICON DIODES Figure 17.1

Figure 17.1 shows the cross section and mechanical structure of the two popular diode glass packages. The double heat sink (DHD) diode is smaller than the conventional (DO-7) glass diode, yet it has a higher dissipation and greater reliability. These are due to the elimination of the "S" spring and fusion of the pellet directly to the Dumet leads. The heat generated in the pellet is dissipated via the leads. This is brought out by Table 17.1 which gives the thermal resistance and power dissipation as a function of the spacing between the heat sink and the end of the diode body.

| HEATSINK<br>SPACING<br>FROM END<br>OF DIODE<br>BODY | STEADY<br>STATE<br>THERMAL<br>RESISTANCE<br>°C/MW |      | POWER<br>DISSIPATION<br>AT 25°C/MW |     |  |

|-----------------------------------------------------|---------------------------------------------------|------|------------------------------------|-----|--|

|                                                     | DO-7                                              | DHD  | DO-7                               | DHD |  |

| .062"                                               | .389                                              | .250 | 450                                | 700 |  |

| .250"                                               | .500                                              | .319 | 350                                | 550 |  |

| .500"                                               | .700                                              | .438 | 250                                | 400 |  |

# DIODE THERMAL RESISTANCE AND POWER DISSIPATION Table 17.1

### DC Characteristics

The characterization of the PEP silicon diode is greatly simplified by the close correlation between the theoretical and the actual parameters. The dc characteristics are generally specified by means of the following parameters and characteristic curves.

# TYPICAL FORWARD DC CHARACTERISTICS OF PEP SILICON DIODES Figure 17.2

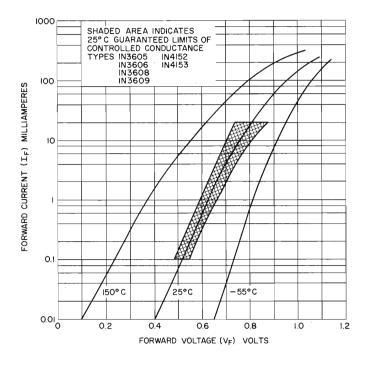

1. Forward Voltage. The maximum value of the forward voltage, V<sub>F</sub>, is generally specified at one or more values of forward current, I<sub>F</sub>. For controlled conductance diodes such as the 1N3605, 6, 8, 9, 1N4152, and 3 both the minimum and maximum

values of forward voltage are specified at six values of forward current. The relationship between the forward voltage and forward current for a typical PEP silicon diode is shown in Figure 17.2 at three values of ambient temperature. The shaded area indicates the guaranteed range of forward characteristics for the controlled conductance types at 25°C junction temperature. The tight control of forward conductance is very desirable in the design of diode logic circuits where it permits greater design margins or additional logic stages. (1)

Forward dc characteristics of the PEP silicon diodes closely follow the theoretical equation

$$I_{F} = I_{S} \left[ \exp \frac{q \left( V_{F} - I_{F} R_{S} \right)}{n K T} - 1 \right]$$

$$(17a)$$

where

Is = diode saturation current

R<sub>s</sub> = diode series ohmic resistance

$q = electronic charge (1.60 \times 10^{-19} coulomb)$

K = Boltzmanns constant  $(1.38 \times 10^{-23} \text{ watt sec/}^{\circ}\text{K})$

T = absolute temperature (°K)

NOTE:

$$I = I_s [exp (x)] = I_s (e^x)$$

.

At low forward currents where  $I_F$   $R_S << V_F$ , and with the exponential term much larger than one, then 17(a) becomes

$$I_{F} = I_{S} \exp \frac{qV_{F}}{\eta KT}$$

17(b)

or

$$V_{F} = \frac{\eta KT}{q} \ln \left( \frac{I_{F}}{I_{s}} \right)$$

17(c)

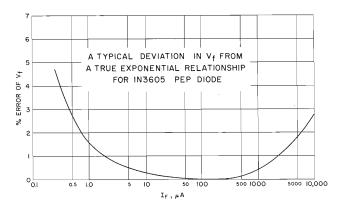

Figure 17.3 shows (5) the deviation of the forward characteristic of a silicon PEP diode from the true exponential equation as given by 17(c). The error is less than 1% from  $2\mu a$  to 2 ma. At low currents the error increases because the exponential term in 17(a) approaches one. At high currents the increase in error is due to the effect of the  $I_F$   $R_S$  term in 17(a).

A TYPICAL DEVIATION IN V, FROM A TRUE EXPONENTIAL RELATIONSHIP FOR 1N3605 PEP DIODE

Figure 17.3

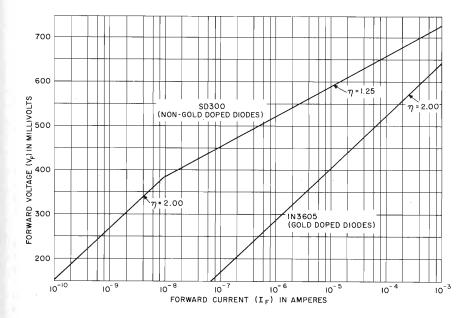

Parameter  $\eta$  in the above equations is dependent upon the impurity gradient in the junction and the carrier lifetime in the semiconductor material. At low values of forward current, carrier recombination in the junction depletion layer is the predominant factor in determining the relationship between forward voltage and current, and  $\eta \cong 2$ . At high values of forward current the relationship between forward current and voltage is determined primarily by minority carrier diffusion, and  $\eta \cong 1$  for nongold doped diodes. The characteristics of the normal gold doped PEP silicon diode can be approximated with reasonable accuracy by assuming that  $\eta = 2$  over the entire current range. (At 25°C this gives  $\eta$ KT/q = .052 volt).  $\eta$  is shown in Figure 17.4 for both gold doped and non-gold doped diodes.

# $\eta$ FOR TWO TYPES OF PEP DIODES Figure 17.4

Dynamic resistance,  $r_{\text{\tiny D}},$  of the diode at a forward current,  $I_{\text{\tiny F}},$  is given by the equation

$$r_D = \frac{\eta KT}{q I_F} + R_S$$

17(d)

Since  $R_s$  is typically 1 to 2 ohms for a PEP diode, the dynamic impedance is inversely proportional to the current up to about 10 ma.

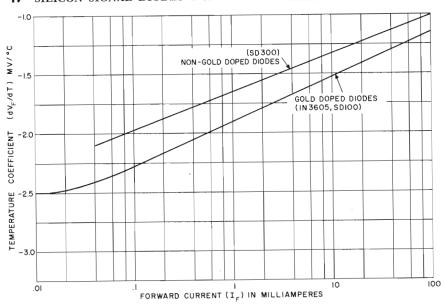

Forward voltage-temperature coefficient can be determined by taking the voltage differential of 17(a) with respect to temperature (remembering that  $I_s$  is a function of temperature). Figure 17.5 shows that for a 1N3605, 1N4152, and SD300, ( $dV_F/dT$ ) is a strong function of forward current.

# V<sub>F</sub> TEMPERATURE COEFFICIENT AS A FUNCTION OF FORWARD CURRENT Figure 17.5

The empirical equations which describes these relations are: for the 1N4152 and 1N3605 series-gold doped diodes

$$\frac{dV_F}{dT} = -1.92 + 0.6 \log_{10} I_F \tag{17e}$$

and for SD300 non-gold doped diodes

$$\frac{\mathrm{dV_F}}{\mathrm{dT}} = -1.66 + 0.33 \log_{10} I_F \tag{17f}$$

where  $I_F$  is in milliamperes and  $dV_F/dT$  is mv/°C. The constant terms in 17(e) and 17(f) are functions of  $I_S$ ,  $\eta$ , and T (the absolute temperature), while the coefficients of the  $\log_{10}I_F$  terms are proportional to  $\eta K/q$ . For germanium the constant term is larger than for silicon, while the coefficient of the log term is small. Thus,  $dV_F/dT$  for germanium is not as strong a function of  $I_F$  as it is with silicon.

- 2. Breakdown Voltage. The breakdown voltage,  $B_v$ , is normally specified at a reverse current of 5  $\mu a$ . The breakdown voltage increases with temperature up to the point where the reverse leakage current becomes comparable with the current at which the breakdown voltage is measured. The breakdown characteristic of a PEP diode may not be as sharp as that of a non-epitaxial diode. The shape of the breakdown characteristic can be explained theoretically, and life tests have shown that this is not as indicative of reliability as it is with other types of diodes.

- 3. Reverse Current. The reverse current,  $I_R$ , is specified at a voltage below the breakdown voltage. The magnitude of the reverse current is dependent on the area of the junction and upon whether the diode has been gold doped or not. Thus, for a given area the  $I_R$  of a non-gold doped unit (SD300) will be two to three orders of magnitude less than the  $I_R$  of a gold doped unit (1N3605). Typical leakage currents

of these two types of diodes at 30 volts and  $25^{\circ}$ C are 0.02 and 20 nanoamperes respectively. Reverse current increases exponentially with temperature as indicated by the equation

$$I_{R} = I_{RO} \exp \delta \left( T - T_{o} \right) \tag{17g}$$

where  $I_R$  is the reverse current at temperature T,  $I_{RO}$  is the reverse current at temperature  $T_o$ , and  $\delta$  is the fractional increase of  $I_R$  with temperature. For the PEP silicon diodes (1N3605, 1N4152)  $\delta \approx 0.055/^{\circ}C$ . The reverse current will increase by a factor of ten when the temperature is increased by  $2.30/\delta = 42^{\circ}C$ . At low values of reverse voltage the reverse current is proportional to the square root of the voltage owing to the spreading of the depletion layer. At values of reverse voltage comparable to the breakdown voltage, the reverse current increases rapidly due to avalanche multiplication and localized breakdown effects.

### AC Characteristics

- 1. Capacitance. The capacitance normally specified for a diode is the total capacitance which is equal to the sum of the junction capacitance and the fixed capacitance of the leads and the package. The capacitance,  $C_0$ , is specified at a frequency of 1 mc with zero applied bias. Since the typical capacitance of some PEP silicon diodes is less than 1.0 pf it is necessary to use a three terminal bridge configuration to achieve an accurate measurement. The junction capacitance is inversely proportional to the square root of the reverse voltage and increases linearly with temperature.

- 2. Rectification Efficiency. The rectification efficiency,  $R_{\text{B}}$ , is defined as the ratio of dc load voltage to peak rf input voltage to the detector circuit, measured with 2.0 volts rms, 100 mc input to the circuit. Load resistance is 5K and the load capacitance is 20 pf. The rectification efficiency is determined primarily by the conductance, reverse recovery time, and capacitance, and provides an indication of the capabilities of the diode as a high frequency detector.

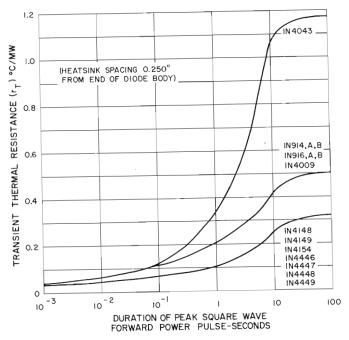

- 3. Transient Thermal Resistance. The transient thermal resistance of a diode is presented by a curve such as Figure 17.6 showing the instantaneous junction temperature as a function of time with constant applied power. This curve permits a determination of the peak junction temperature under any type of pulsed operation. By means of a simple analytical procedure, described in Reference 2, this curve can be used to determine the peak junction temperature under any type of transient operation and hence provides a valuable method of insuring the reliable operation of diodes in pulse circuits. (2)

- 4. Forward Recovery Time. If a large forward current is suddenly applied to a diode, the voltage across the diode will rise above its steady state value and then drop rapidly, approaching the steady state value in approximately an exponential manner. This effect is caused by the finite time required to establish the minority carrier density on both sides of the junction. The forward recovery time is the time required for the diode voltage to drop to a specified value after the application of a step of forward current. The forward recovery time increases for a given area device as the breakdown voltage increases and the capacitance decreases (increasing resistivity), and as the reverse recovery time decreases (decreasing lifetime). Under some extremes of resistivity and lifetime, the forward recovery time can be longer than the reverse recovery time. For a given diode the forward recovery time also increases as the rate of rise of the forward current is increased, and decreases as the forward current flowing prior to the current step is increased. If the amplitude of the forward current step is sufficiently small the effect of the junction capacity will predominate and prevent the diode voltage from overshooting its steady state value.

# MAXIMUM TRANSIENT THERMAL RESISTANCE Figure 17.6

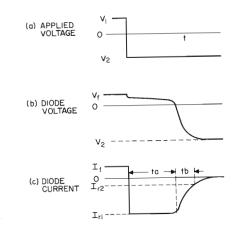

TYPICAL DIODE REVERSE TRANSIENT WAVEFORMS

Figure 17.7

5. Reverse Recovery Time. When a forward biased diode is subjected to a reverse voltage step, a large reverse current will flow for a short time as a result of the stored charge consisting of the minority carriers on both sides of the junction. The typical

voltage and current waveforms involved as shown in Figure 17.7. Initially, a current  $I_F$  is flowing in the diode and a voltage  $V_F$  appears across it. When the reverse voltage step occurs at t=0 a reverse current  $I_{r1}$  flows which is determined by the magnitude of the applied voltage and the loop impedance of the circuit. At the same time the forward voltage decreases by an amount approximately equal to  $R_S$  ( $I_F + I_{r1}$ ) due to the reversal of the current through the diode. The reverse current remains constant at  $I_{r1}$  for a time  $t_a$  (the constant current phase) and then rapidly decreases, approaching the dc reverse current value. At the same time the diode voltage goes negative and approaches the value of the applied reverse voltage.

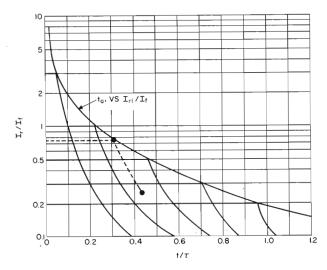

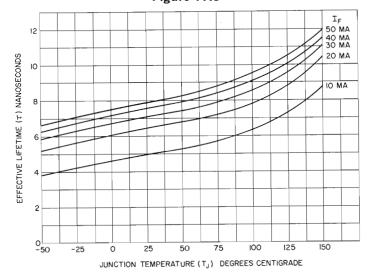

The reverse recovery time of a diode,  $t_{r\tau}$ , is specified as the time between the application of reverse voltage and the point where the reverse current has dropped to a specified value,  $I_{r\tau}$ . The specification must also include the forward current,  $I_{F\tau}$ , the initial reverse current,  $I_{\tau\tau}$ , and the loop impedance of the test circuit. The specification of the reverse recovery time of diodes is difficult to use for circuit design purposes because the recovery time is given only for one arbitrary test circuit and bias condition. Due to the wide variety of possible circuit arrangements and bias conditions encountered in diode applications, it is impossible for the manufacturer to control and specify the reverse recovery time corresponding to each special condition encountered. However, for most design requirements an accurate estimation of the reverse recovery time can be obtained by use of a quantity called the *effective lifetime*,  $\tau$ , and the ratio of the forward and reverse currents. Figure 17.8 can be used for this purpose together with Figure 17.9 which gives the typical effective lifetime of the PEP silicon diode as a function of temperature for various values of forward current.

The use of Figure 17.8 and 17.9 in estimating the reverse recovery time of a PEP silicon diode can be best described by means of the following design example.

Problem: Estimate the typical recovery time to 5 ma reverse current (I<sub>R2</sub>) when the forward current is 20 ma (I<sub>F</sub>) and the initial reverse current is 15 ma (I<sub>Tl</sub>) at a temperature of 75°C.

Solution: Enter the left side of Figure 17.8 at  $I_{r1}/I_{\rm f}=15/20=0.75$  and follow horizontally (dotted line) until the  $t_{\rm a}$  vs.  $I_{\rm r1}/I_{\rm f}$  line is reached. From the  $t/\tau$  scale on the horizontal axis, it is seen that  $t_{\rm a}=0.31\tau$ . The  $t_{\rm b}$  portion of the curve is estimated by moving downward parallel to the general contour lines until reaching the line corresponding to  $I_{\rm r2}/I_{\rm f}=5/20=0.25$ . The total switching time is thus  $0.44\tau$ . From Figure 17.9 the effective lifetime at  $I_{\rm F}=20$  ma and  $T_{\rm J}=75\,^{\circ}{\rm C}$  is 6.0 nsec, hence the calculated values are

constant current phase  $t_n = (0.31) (6.0) = 1.86$  nsec. reverse recovery time  $t_{rr} = (0.44) (6.0) = 2.64$  nsec.

For additional material on the reverse recovery time of diodes see References 3 and 4.

6. Stored Charge. Increasing use is being made of stored charge, Q<sub>8</sub>, as a parameter for characterizing the reverse recovery time of diodes. For a given diode type and structure there is a direct correlation between the reverse recovery time in a given circuit to a given set of conditions and the stored charge so that the two measurements are equivalent. However, the use of stored charge as the specified parameters offers a number of significant advantages over the use of reverse recovery time.

- Stored charge is a single unambiguous figure of merit for a diode which can

be specified without an elaborate set of test conditions and test jig construction

details. It is generally sufficient to specify only the forward current at which the

stored charge is measured.

- The test circuit for measurement of stored charge is simple and relatively inexpensive. A direct meter readout is possible even with high speed diodes, and the use of an expensive sampling scope is avoided.

# 17 SILICON SIGNAL DIODES & SNAP DIODES

- Reproducibility of stored charge measurements are better than the reproducibility of reverse recovery time measurements.

- 4. Comparative reading of stored charge can be made even on ultra-fast recovery diodes which can not be measured on the fastest sampling scopes.

CURVE FOR DETERMINING REVERSE RECOVERY

TIME UNDER VARIOUS DRIVE CONDITIONS

Figure 17.8

EFFECTIVE LIFETIME OF PEP SILICON DIODES VS. TEMPERATURE AND FORWARD CURRENT Figure 17.9

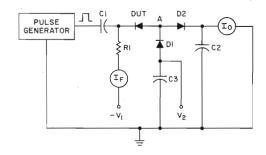

# BASIC DIODE STORED CHARGE TEST CIRCUIT Figure 17.10

The basic circuit for measurement of stored charge is shown in Figure 17.10. In this circuit the diode under test (DUT) is biased by a forward current which flows through D1, the DUT, R1, and the bias current meter  $I_F$ . A short positive pulse at a known frequency, f, is coupled from the pulse generator through C1 to the DUT. This pulse reverse biases the DUT and forces the charge stored on the DUT through D2 into the output current meter  $I_0$ . The current through the meter  $I_0$  will be proportional to the charge stored on the DUT. If the forward voltage across the DUT is set to zero by adjusting  $V_1$ , an output current  $I_1$  will flow which is proportional to the capacitance of the DUT.

$$I_{z} = f V_{P} C_{avg} + f t_{P} I_{r}$$

$$(17h)$$

where f is the pulse frequency,  $V_p$  the amplitude of the pulse,  $C_{avg}$  the average capacitance of the diode over the range of reverse voltage from 0 to  $V_p$ ,  $t_p$  the pulse width, and  $I_r$  the reverse leakage current of the DUT measured at a reverse voltage equal to  $V_p$ . The storage charge is defined by the equation

$$Q_s = \frac{I_2 - I_1}{f} \tag{17i}$$

where  $I_2$  is the output current at the specified value of forward current, and  $I_1$  the output current with a zero bias voltage across the DUT. Inasmuch as the above definition of  $Q_8$  involves the difference between two bias conditions it reduces the dependance of the measurement on the pulse voltage and the reverse current of the DUT, and thus provides a more significant parameter for characterizing the diode. Effects of leakage current, junction capacitance, pulse amplitude and pulse width can be considered separately by the designer when estimating the performance of a diode in a given circuit.

Certain precautions must be observed when building and using the test circuit of Figure 17.10 for measurements on high speed diodes. The pulse generator must have a fast rise-time. It is particularly important that the 0 to 10% rise-time of the pulse be short to prevent losing part of the stored charge before the voltage has reached the level required to forward bias D2. The pulse generator should have a high output voltage and a low output impedance so that a large reverse current can be forced through the DUT resulting in a minimum amount of stored charge being lost through recombination. Diode D1 should be an ultra-fast recovery type since any charge store on D1 will subtract from  $Q_s$  of the DUT. However, the reading for  $Q_s$  of the DUT can be corrected if  $Q_s$  of D1 is known. Diode D2 must be a diode with fast turn-on, low leakage, a moderately low  $Q_s$ , and a high conductance and pulse current capability

to permit the flow of the large reverse current of the DUT. The voltage V2 should be adjusted at the different measurement condition to maintain the voltage at point A constant. If this is not done a portion of Qs will be lost owing to the capacitance between point A and ground together with the difference in voltage required at point A to forward bias D2. Likewise the output current meter must have a sufficiently low resistance to avoid an appreciable change in voltage across C2 at the different measurement conditions. In the construction of the test circuit particular care should be taken in minimizing the inductance through C1, the test clips, the DUT, D2, C2, D1, and C3. Typical test conditions for measurement of high speed diodes would be: f = 100 kc,  $V_p = 10 \text{ volts}$ ,  $t_p = 100 \text{ nanoseconds}$ ,  $t_r = 0.3 \text{ nanoseconds}$ , and  $I_F$ = 10 milliamperes.

The test circuit, the definition of stored charge, and the measurement precautions given above are essentially equivalent to those given in the IS-2 proposed standard on stored charge, and in method 4062 of MIL-STD-750.

For a given type of diode the stored charge is directly related to the effective lifetime, r, and to the reverse recovery time in a given test circuit with a given set of test limits. The relationship between stored charge and effective lifetime for the 1N3605, 1N4152 family of diodes is given by  $\tau \approx 1.5$  (O<sub>5</sub>/I<sub>F</sub>), where I<sub>F</sub> is the current at which Qs is measured or specified. Using this relationship and the curves given in Figure 17.8 it is possible to predict the reverse recovery time from the stored charge value. For example, assume a 1N3605 diode has a stored charge of 35 picocoulombs measured at I<sub>F</sub> = 10 ma and it is desired to determine the reverse recovery time, t<sub>rr</sub>, for  $I_f = 10$  ma,  $I_{r1} = 10$  ma, and  $I_{r2} = 1$  ma. The effective lifetime is

$\tau = 1.5 \ (35/10) = 5.25 \ \text{nanoseconds}$

and from Figure 17.8

$t_{rr} = 0.57\tau = 3.0$  nanoseconds

#### Diode Comparisons and Trade-Offs

As in all designs, the design of a diode to perform a given function requires a series of compromises. An improvement in one parameter is usually accompanied by the deterioration of another parameter. This can be seen in Table 17.2 where the important parameters are shown for a series of diodes with different areas, levels of gold doping, and resistivities. Junction areas of the SD100, SD300, and SD500 are the same, while the junction area of the SD600 and SD800 are twice and fourteen times the area of the SD100, respectively. Gold doping levels for the SD100, SD500, and SD600 are approximately the same, while the SD400 has less; the SD800 is only lightly doped and the SD300 has none. Resistivities of all the diodes are about the same with the exception of the SD500. It has a higher resistivity which increases the breakdown voltage and reduces the capacitance of the diode. This, however, is accomplished at the expense of the reverse recovery time.

Notice that the SD300 which has no gold doping has a much lower leakage current than the SD100 and a higher conductance; however, it has a slightly larger capacitance and a much higher reverse recovery time.

The increasing conductance of the SD600, SD400, and SD800 is due to the increasing areas of these diodes. The price paid for this is an increase in capacitance and recovery time. Because of the successive lighter levels of gold doping used as the device area is increased, the leakage current of these devices does not increase in proportion to the increase in area.

A parameter not shown in Table 17.2 is forward recovery time. However, as was pointed out earlier in this chapter, the forward recovery time may increase as the level of gold doping is increased (reverse recovery lowered) and as the resistivity is increased (breakdown voltage increased).

| DEVICE                                                                           | SD100                         | SD500                    | SD300         | SD600            | SD400 | SD800 | UNITS             |

|----------------------------------------------------------------------------------|-------------------------------|--------------------------|---------------|------------------|-------|-------|-------------------|

| Junction Area                                                                    | A                             | A                        | A             | 2Å               | 5.7A  | 14A   |                   |

| Gold                                                                             | Yes                           | Yes                      | No            | Yes              | Yes   | Yes*  | ,                 |

| Resistivity                                                                      | Mod.                          | High                     | Mod.          | Mod.             | Mod.  | Mod.  |                   |

| Breakdown<br>Voltage                                                             | 60-90                         | 90-160                   | 60-90         | 60-90            | 60-90 | 60-90 | volts             |

| Max. Leakage<br>Currents @ 30<br>volts, 25°C                                     | 30                            | 30                       | 0.1<br>at 10V | 50               | 50    | 50    | nano-<br>amps     |

| Capacitance at 0 volts                                                           | 1-2                           | 0.6-1.4                  | 2-4           | 2-5              | 4-9   | 15-30 | pico-<br>farads   |

| Reverse Recovery<br>Time $t_{rr}$ ( $I_R = I_F$<br>= 10 ma, recovery<br>to 1 ma) | 2-4                           | 3-5                      | 100           | 2-4              | 6-10  | 10-18 | nano-<br>seconds  |

| Conductance<br>I <sub>F</sub> at V <sub>F</sub> = 1 volt<br>@ 25°C               | 100                           | 100                      | 150           | 250              | 500   | 900   | milli-<br>amperes |

| JEDEC<br>Registered<br>Types                                                     | 1N3604-68<br>1N4009<br>1N4154 | 1N914<br>1N914B<br>1N916 |               | 1N3600<br>1N4150 |       |       |                   |

<sup>\*</sup>Lightly doped

# COMPARISON OF DIODE CHARACTERISTICS **Table 17.2**

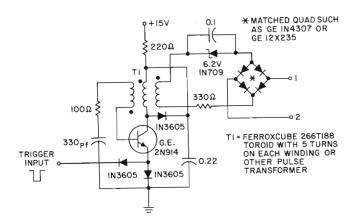

## DIODE ASSEMBLIES

PEP silicon diodes are available in matched pairs and matched quads for use in applications where close matching in the forward characteristics is required. These units are sealed in small epoxy packages to preserve the identity of the diodes and minimize temperature differentials between diodes. The diodes used in these assemblies have all of the high performance capabilities of the standard PEP silicon diodes, and in addition are matched within very tight limits for V<sub>F</sub> over a range of forward currents and over a wide temperature range. V<sub>F</sub>'s are matched to better than 10 my (3 mv typical) from 100 μa to 10 ma and to better than 20 mv from 10 ma to 50 ma over the entire temperature range of  $-55^{\circ}$ C to  $+125^{\circ}$ C. Further, diode pellets can be assembled into any configuration in multi-leaded TO-5, TO-18, and flat packages. The degree of matching V<sub>F</sub> for pairs or quads of pellets can be as good or better than obtained with the diode assemblies already discussed.

An example of the application of a diode matched quad in a sampling bridge circuit is shown in Figure 17.11. A negative pulse at the input will trigger the blocking oscillator generating a pulse approximately 100 nanoseconds wide. The pulse at the output winding will forward bias the diodes in the bridge with a current of approximately 20 milliamperes. This produces the effect of a closed contact between terminals 1 and 2 with a typical impedance of 5 ohms, and a typical offset voltage of less than 2 millivolts. Between pulses the bridge diodes are reverse biased by the charge on the 0.1 µfd capacitor, and the equivalent impedance between terminals 1 and 2 is typically 1000 megohms.

DIODE SAMPLING BRIDGE WITH BLOCKING OSCILLATOR DRIVING CIRCUIT **Figure 17.11**

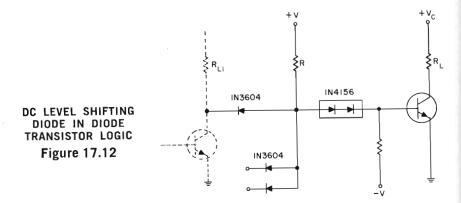

## **STABISTORS**

Stabistors are single or multi-pellet diodes which have tightly controlled forward voltage characteristics and which are always used in a forward biased condition. Two examples of the multi-pellet stabistor (or low voltage reference diode) are the 1N4156 and 1N4157. The 1N4156 contains two diode pellets in a single glass package while the 1N4157 contains three diode-pellets in a single glass package. Both have a tightly controlled V<sub>F</sub> characteristic over an I<sub>F</sub> range of .01 to 100 ma. Stabistors are used as low voltage regulator diodes, as amplifier non-linear bias elements, and as a level shifting diode in diode-transistor logic circuits such as shown in Figure 17.12. When the multi-pellet stabistor is used as a low voltage regulator, the temperature coefficient of the stabistor will be larger than a breakdown diode of comparable voltage. However, this is offset by the stabistor's tighter initial tolerance, lower dynamic impedance, and absence of noise at low currents.

## SNAP DIODES

The normally undesirable recovery characteristics of a conventional diode are improved and controlled in the snap diode. This results in a device ideally suited for highly efficient harmonic generators and pulse generators with extremely short transition times.

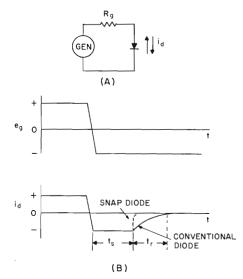

Under conditions of forward bias the diode will store a finite amount of charge. The amount stored is primarily dependent upon the lifetime of the material and the magnitude of the forward current. If the diode is suddenly reverse biased, after having been forward biased, it will conduct in the reverse direction for a finite time until all carriers stored in the diode have been removed as shown in Figure 17.13. The length of time the reverse current flows (storage time) is a function of the initial charge stored, the diode lifetime, and the amount of reverse current. As soon as the stored charge at the junction goes to zero, the diode begins to turn off. A well designed snap diode will turn off linearly as shown in Figure 17.13. This is in contrast to the complex error function turn-off characteristic of a conventional high-speed planar epitaxial diode.

REVERSE RECOVERY OF A DIODE **Figure 17.13**

Turn-off or snap-off time is a function of carrier gradient at the junction, diode capacitance, package inductance, initial charge stored, and loop impedance. It is therefore difficult for the circuit designer to calculate the turn-off time. Circuit and package inductances and capacitances should be minimized, however, and the loop impedance adjusted to minimize the turn-off time. (If the impedance is too low, the L/R time constant becomes too large, while if it too large, the RC time constant predominates.)

Turn-off time is generally given on the specification sheet for a particular set of forward and reverse currents. Thus, the SSA550 and SSA551 snap diodes have a maximum snap-off time of 0.5 nanoseconds for a forward current of 1 ma and a reverse current of 20 ma. Snap-off time may be limited by the package, circuit, or test equipment. For example, the SSA552 and SSA553 have a typical snap-off time given as 0.2 nanoseconds. This figure is probably limited by the package inductance and test equipment available at the time of measurement. For extremely short snap-off times, the SSA556 and SSA557 should be used since these units have a "pill" package construction with only 0.15 nanohenries of inductance. They have been tested in strip line circuits where the snap-off time has been measured as 0.1 nanoseconds using a sampling scope of 0.1 nanosecond rise-time.

While it is difficult to predict the snap-off time, the charge stored during forward bias and the storage-time under reverse bias conditions are easily calculated. The charge stored can be obtained by solving the charge continuity equation

$$\frac{\mathrm{dQ}}{\mathrm{dt}} = i_{\mathsf{d}} - Q/\tau \tag{17i}$$

where  $i_d$  is the conduction current across the junction and  $\tau$  is the recombination lifetime.

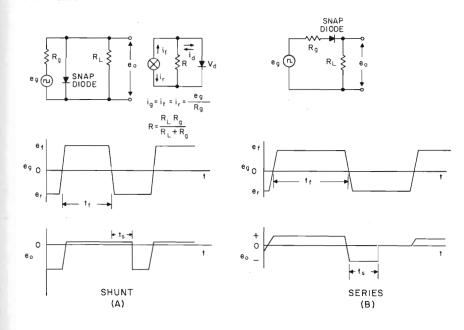

For the case of a rectangular supply voltage with the shunt and series circuit of Figure 17.14, the stored charge becomes.

$$Q_{t} = \tau(i_{t} - \frac{v_{d}}{R}) (1 - e^{-t_{f}/\tau})$$

(17j)

where

$$i_f = \frac{e_g}{R_g}$$

and

$$R = \frac{R_g R_L}{(R_g + R_L)}$$

for the shunt circuit;

and

$$i_{\text{f}} = \frac{e_{\text{g}}}{R_{\text{g}} + R_{\text{L}}}$$

and

$R=R_g+R_L$  for the series circuit. If  $t_f>>\tau$  the stored charge becomes

$$Q_{t} = \left(i_{t} - \frac{v_{d}}{R}\right)\tau \tag{17k}$$

The storage-time,  $t_s$ , is also obtained by solving equation (17i) for the charge recovered under reverse bias conditions.\* The charge thus recovered is

$$Q_{r} = \tau \left( i_{r} + \frac{v_{d}}{R} \right) - Q_{r}e^{-t/\tau}$$

(171)

where

$$i_r = \frac{e_r}{R_g}$$

for the shunt circuit;

and

$$i_r = \frac{e_r}{(R_e + R_L)}$$

for the series circuit.

When  $Q_r$  goes to zero the diode snaps off so that the storage-time  $t_s$  is obtained from equation (171) as

$$t_{s} = \tau \ln \left[ \frac{Q_{r}}{\tau \left( i_{r} + \frac{v_{d}}{R} \right)} \right] \tag{17m}$$

The series circuit provides a convenient method of measuring the diodes lifetime. If the forward bias current is applied for a time much larger than the diodes lifetime, and the reverse current is of sufficient amplitude that the storage-time is much less

than the lifetime, then the lifetime can be calculated to be

$$\tau = \left(\frac{i_{Lr}}{i_{Lf}}\right) t_s \tag{17n}$$

Thus it is only necessary to measure the two currents and the storage-time to calculate the lifetime.

# SERIES AND SHUNT CIRCUIT WITH RECTANGULAR SUPPLY Figure 17.14

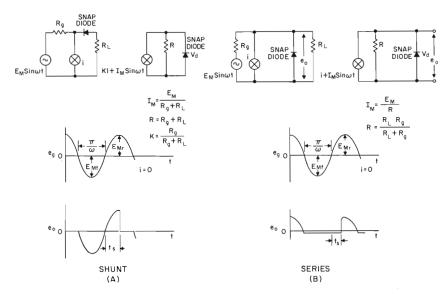

If a sinusoidal supply is used with a rectangular and dc current, then the charge stored for the series and shunt circuit of Figure 17.15 is

$$Q_{t} = \tau \left( i - \frac{v_{d}}{R} \right) (1 - e^{-\pi/\omega \tau}) + \frac{\omega I_{Mt}}{\left(\frac{1}{\tau}\right)^{2} + \omega^{2}} (1 + e^{-\pi/\omega \tau})$$

(170)

where

$$R = \frac{R_g R_L}{(R_g + R_L)}$$

and

$$I_{Mf} = \frac{E_{Mf}}{R_g}$$

for the shunt circuit;

and

$$R = R_g + R_L$$

and

$$I_{Mt} = \frac{E_{Mt}}{R_g + R_L}$$

for the series circuit.

For the case where  $\pi/T << \omega$ , then the charge stored becomes

$$Q_{\rm f} = 2 \, I_{\rm Mf}/\omega \tag{17p}$$

<sup>\*</sup>Because of the method of manufacture, over 95% of the charge is recovered during the storage time. This is not true for a conventional diode.

SERIES AND SHUNT CIRCUITS WITH SINEWAVE SUPPLY Figure 17.15

The charge recovered during the half cycle of reverse bias becomes

$$\begin{split} Q_R &= \left(\tau K i_r + \frac{\tau v_d}{R} + Q_t - \frac{\omega I_{Mr}}{(1/\tau)^2 + \omega^2}\right) e^{-t/\tau} - \tau K i_r - \frac{\tau v_d}{R} \\ &- \frac{I_{Mr} \sin \omega t}{\tau \left[\left(\frac{1}{\tau}\right)^2 + \omega^2\right]} + \frac{\omega I_{Mr}}{\left(\frac{1}{\tau}\right)^2 + \omega^2} \cos \omega \end{split} \tag{17q}$$

where

K = 1 for the shunt circuit and

$$K = \frac{R_g}{(R_L + R_g)} \text{ for the series circuit. If } \pi/\omega << \tau \text{ then}$$

$$Q_R = Q_f - I_{Mr}/\omega \text{ (1-cos } \omega t\text{)}$$

(17r)

Equations (17p) and (17r) can be combined to give the snap off angle  $\theta = \cos^{-1} (1 - 2 I_{Mf}/I_{Mf})$

If the peak forward and reverse currents are equal,  $\theta = 180^{\circ}$ . Some form of self bias or different values of current must be used if the diode is to snap off before reaching 180°. On the other hand if the above inequality does not hold, then the diode will snap off at some angle before 180° even if the forward and reverse peak currents are equal.

Because of a larger lifetime (20-100 nanoseconds) the SSA550, SSA551, SSA554, and SSA555 should be used when the frequency is roughly below 100 mc. The reason is that a larger charge can be stored during the half cycle of forward bias which in turn allows a larger reverse peak current. Above about 100 mc it is desirable to use the SSA552, SSA553, SSA556 and SSA557 with lifetimes of 1-5 nanoseconds, otherwise all the stored charge might not be removed during the time of reverse bias without an excessively high peak reverse current.

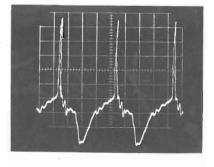

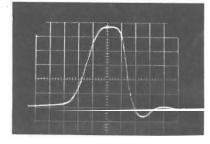

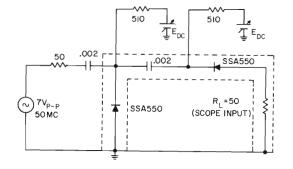

Figure 17.16 shows a simple pulse generator which utilizes a sinusoidal supply and a shunt-series circuit. The pulse width and its phase relationship with the 50 mc

source are adjustable by means of the dc voltages. The rise and fall times are probably inductance limited. The construction details, together with other configurations are given in Reference 6.

H = 2 nsec/CMV = 0.5 V/CM

H = 2 nsec/CMV = 0.5 V/CM

TIME →

SHUNT-SERIES PULSE CIRCUIT RESPONSE Figure 17.16

### **REFERENCES**

- (1) Kvamme, E.F., "Controlled Conductance Applications," General Electric Application Note 90.40.

- (2) Gutzwiller, F.W., Sylvan, T.P., "Power Semiconductor Ratings Under Transient and Intermittent Loads," General Electric Application Note 200.9.

- (3) Chen, C.H., "Predicting Reverse Recovery Time of High Speed Semiconductor Diodes," General Electric Application Note 90.36.

- (i) Ko, W.H., "The Reverse Transient Behavior of Semiconductor Junction Diodes," IRE Transactions, ED-8, March 1961, pp. 123-131.

- (5) Giorgis, J., "The Logarithmic and Temperature Coefficient Characteristics of the 1N3605 and 1N3606 Diode," General Electric Application Note 90.47.

- (6) Giorgis, J., "Understanding Snap Diodes," Electronic Equipment Engineering, November 1963.