Thanks for the informative explanation as usual.

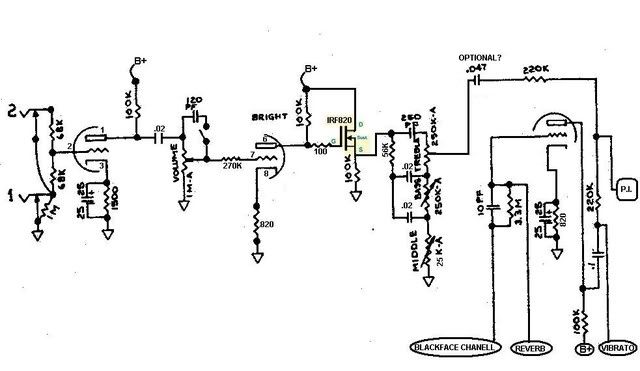

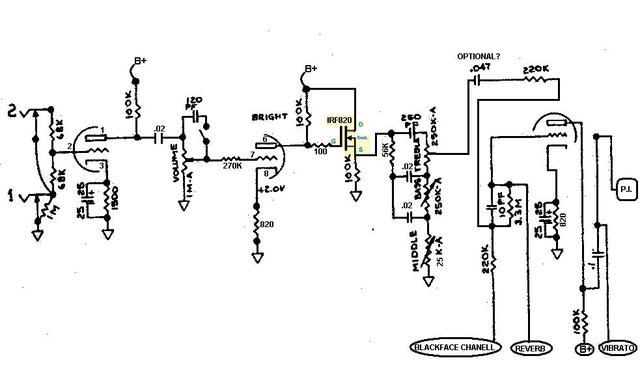

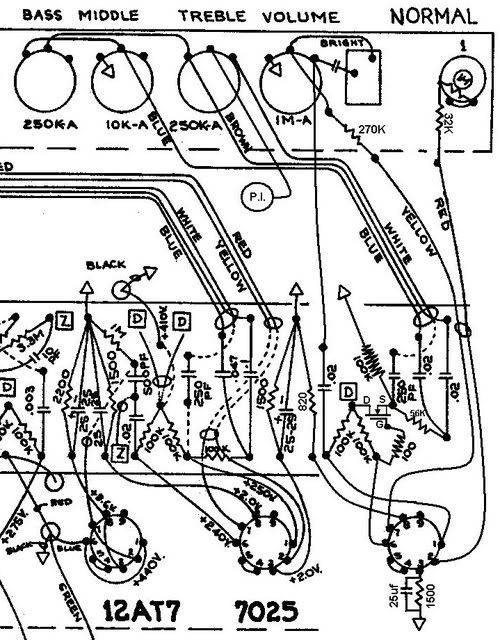

For those of us who are not very much into theory dose it mean that 33k is too low or too high for SF source resistor? I'm currently running this SF at 363V, 173V at the source.

Running the source resistor up makes it easier for the preceeding stage to drive the high gate-source capacitor at all frequencies and I think that's what happened for you.

)

)

)

)

Comment