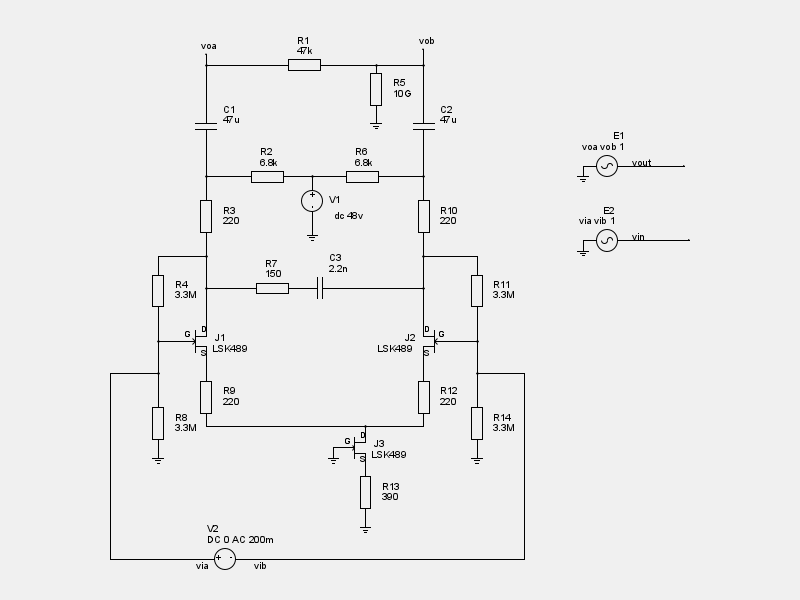

I want to build the Alex Rice Piezo Preamp (Alex Rice Piezo Preamplifier | Zach Poff (schematic included)), but need to match the JFETs.

I've found several ways to do this on the Internet, but all require extra parts which I don't have right now. Someone suggested that the matching setup must be as close as possible to the real setup.

So I thought: Is it possible to just build the preamp on a breadboard (which I do have) and use that to match the JFETs?

And if so what do I have to measure?

And if this is not possible, what would be the best alternative?

Thanks in advance.

Hans

I've found several ways to do this on the Internet, but all require extra parts which I don't have right now. Someone suggested that the matching setup must be as close as possible to the real setup.

So I thought: Is it possible to just build the preamp on a breadboard (which I do have) and use that to match the JFETs?

And if so what do I have to measure?

And if this is not possible, what would be the best alternative?

Thanks in advance.

Hans

. You need to add the input capacitors and provide the input signal(s) in a slightly different way.

. You need to add the input capacitors and provide the input signal(s) in a slightly different way.

Comment